# Digital ASIC Fabrication

## Design Document for Team sdmay26-24

Colin McGann - Project Lead

Samuel Forde - PCB & Layout Lead

Michael Drobot - Firmware Lead

Jack Tonn - Testbench and Validation Lead

Dawud Benedict - Toolflow Lead

Emil Kusic - Repository and Coding Standards Lead

Joshua Arceo - Client/Advisor Communications Lead

Team Email: sdmay26-24@iastate.edu

Team Website: sdmay26-24.sd.ece.iastate.edu

Revised: November 19, 2025– Version 0.1

# Executive Summary

# Learning Summary

## Development Standards & Practices Used

### Summary of Requirements

### Applicable Courses from Iowa State University Curriculum

- CPRE 281 - Digital Logic

- CPRE 288 - Embedded Systems I

- EE 330 - Integrated Electronics

- COMS 336 - Introduction to Computer Graphics

- CPRE 381 - Computer Organization and Assembly Level Programming

- EE 465 - Digital VLSI Design

- CPRE 487 - Hardware Design for Machine Learning

- CPRE 488 - Embedded Systems Design

- CPRE 581 - Computer Systems Architecture

### New Skills/Knowledge not Taught in Courses

- Tools

- GTKWave

- KLayout

- OpenROAD

- OpenLANE

- Skills

- ASIC Design

-

- Knowledge Gained

-

# Contents

|       |                                                                                                                                    |    |

|-------|------------------------------------------------------------------------------------------------------------------------------------|----|

| 1     | Introduction                                                                                                                       | 10 |

| 1.1   | Problem Statement                                                                                                                  | 10 |

| 1.2   | Intended Users                                                                                                                     | 10 |

| 1.2.1 | Embedded GPU Users                                                                                                                 | 10 |

| 1.2.2 | Chipforge Members                                                                                                                  | 10 |

| 1.2.3 | ISU Faculty                                                                                                                        | 11 |

| 2     | Requirements, Constraints, and Standards                                                                                           | 12 |

| 2.1   | Requirements & Constraints                                                                                                         | 12 |

| 2.2   | Engineering Standards                                                                                                              | 13 |

| 2.2.1 | <u>IEEE 1364.1-2002</u> : IEEE Standard for Verilog Register Transfer Level Synthesis                                              | 13 |

| 2.2.2 | <u>IEEE 1364-2001</u> : IEEE Standard Verilog Hardware Description Language                                                        | 13 |

| 2.2.3 | <u>IEEE 1149.7-2009</u> : IEEE Standard for Reduced-Pin and Enhanced-Functionality Test Access Port and Boundary-Scan Architecture | 13 |

| 3     | Project Plan                                                                                                                       | 14 |

| 3.1   | Project Management/Tracking Procedures                                                                                             | 14 |

| 3.2   | Task Decomposition                                                                                                                 | 14 |

| 3.3   | Project Proposed Milestones, Metrics, and Evaluation Criteria                                                                      | 16 |

| 3.4   | Project Timeline/Schedule                                                                                                          | 16 |

| 3.5   | Risks and Risk Management/Mitigation                                                                                               | 18 |

| 3.6   | Personnel Effort Requirements                                                                                                      | 19 |

| 3.7   | Other Resource Requirements                                                                                                        | 19 |

| 4     | Design                                                                                                                             | 20 |

| 4.1   | Design Context                                                                                                                     | 20 |

| 4.1.1 | Broader Context                                                                                                                    | 20 |

| 4.1.2 | Prior Work/ Solutions                                                                                                              | 21 |

| 4.1.3 | Technical Complexity                                                                                                               | 22 |

|           |                                  |    |

|-----------|----------------------------------|----|

| 4.2       | Design Exploration               | 22 |

| 4.2.1     | Design Decisions                 | 22 |

| 4.2.2     | Ideation                         | 23 |

| 4.2.3     | Decision-Making and Trade-Off    | 24 |

| 4.3       | Proposed Design                  | 24 |

| 4.3.1     | Overview                         | 24 |

| 4.3.1.1   | Input Processing                 | 26 |

| 4.3.1.2   | Shader Cores                     | 27 |

| 4.3.1.2.1 | Vertex Shading                   | 28 |

| 4.3.1.2.2 | Fragment Shading                 | 34 |

| 4.3.1.3   | Rasterization                    | 35 |

| 4.3.1.4   | Buses, Memory, and Controls      | 37 |

| 4.3.1.5   | VGA Output                       | 37 |

| 4.3.1.6   | Hardware                         | 37 |

| 4.3.2     | Functionality                    | 39 |

| 4.3.3     | Areas of Concern and Development | 39 |

| 4.4       | Technology Considerations        | 40 |

| 4.5       | Design Analysis                  | 40 |

| 5         | Testing                          | 41 |

| 5.1       | Unit Testing                     | 41 |

| 5.2       | Interface Testing                | 41 |

| 5.3       | Integration and System Testing   | 41 |

| 5.4       | Regression Testing               | 42 |

| 5.5       | Acceptance Testing               | 42 |

| 5.6       | User Testing                     | 44 |

| 5.7       | Results                          | 45 |

| 5.8       | Post-Tapeout Validation          | 45 |

| 6         | Implementation                   | 46 |

|       |                                                               |    |

|-------|---------------------------------------------------------------|----|

| 7     | Ethics and Professional Responsibility . . . . .              | 47 |

| 7.1   | Areas of Professional Responsibility/Code of Ethics . . . . . | 47 |

| 7.2   | Four Principles . . . . .                                     | 47 |

| 7.3   | Virtues . . . . .                                             | 47 |

| 8     | Closing Material . . . . .                                    | 48 |

| 8.1   | Conclusion . . . . .                                          | 48 |

| 8.2   | References . . . . .                                          | 48 |

| 8.3   | Appendices . . . . .                                          | 48 |

| 8.3.1 | Further Reading . . . . .                                     | 48 |

| 9     | Team . . . . .                                                | 50 |

| 9.1   | Team Members . . . . .                                        | 50 |

| 9.2   | Required Skill Sets for your Project . . . . .                | 50 |

| 9.3   | Skill Sets Covered by the Team . . . . .                      | 50 |

| 9.4   | Project Management Style Adopted by the Team . . . . .        | 50 |

| 9.5   | Initial Project Management Roles . . . . .                    | 50 |

| 9.6   | Team Contract . . . . .                                       | 50 |

## List of Figures

|    |                                                                                                                                                                              |    |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1  | $\mu$ GPU Data Flow . . . . .                                                                                                                                                | 25 |

| 2  | Vertex and Index Buffer Entries for 3D Models . . . . .                                                                                                                      | 26 |

| 3  | Vertex Shading Steps . . . . .                                                                                                                                               | 28 |

| 4  | Viewing frustum, showing $zNear$ , $zFar$ , and clipping . . . . .                                                                                                           | 31 |

| 5  | A bounding box around a triplet of vertices . . . . .                                                                                                                        | 35 |

| 6  | Calculation of the barycentric coordinates for a triangle defined by $(x_0, y_0)$ , $(x_1, y_1)$ , $(x_2, y_2)$ and a point $(x, y)$ . . . . .                               | 36 |

| 7  | Calculation of the depth of a pixel within the rasterized triangle. . . . .                                                                                                  | 36 |

| 8  | Calculation of the texture address for a pixel within a triangle. $(u_{0-2}, v_{0-2})$ are the texture coordinates defined at the 3 corners of the current triangle. . . . . | 36 |

| 9  | VGA output module block diagram . . . . .                                                                                                                                    | 38 |

| 10 | VGA color resistor ladder . . . . .                                                                                                                                          | 38 |

| 11 | 3D render of MemoryVGAPmod . . . . .                                                                                                                                         | 39 |

| 12 | Monitor artifacts during FPGA testing . . . . .                                                                                                                              | 42 |

## List of Tables

|   |                                                               |    |

|---|---------------------------------------------------------------|----|

| 1 | Project Risks . . . . .                                       | 18 |

| 2 | Personnel Effort Requirements . . . . .                       | 19 |

| 3 | Broader Context . . . . .                                     | 21 |

| 4 | Model Transformation Matrices . . . . .                       | 30 |

| 5 | Test models and required performance, by complexity . . . . . | 44 |

| 6 | Test model performance results . . . . .                      | 45 |

## Definitions

**Bringup** Testing and developing software for a finished and taped out design.

**Caravel** The platform provided by ChipFoundry that contains our design. Includes a RISC-V core, IO protections, memory for the RISC-V core, a Wishbone IO bus, UART, and

SPI.

**Connectivity** How the vertices of a model are connected together to form triangles.

**Fragment** A single pixel outputted by the rasterizer.

**Framebuffer** Region in memory that holds a frame of video. The frame could be in progress or complete.

**GPU** Graphics Processing Unit. Dedicated hardware to accelerate graphics calculations.

**GPU Memory** The external QSPI memory used for model, texture, and framebuffer storage.

**Hardening** Compiling a hardware design into fabrication files containing the silicon traces on the die.

**Index Buffer** List of indices in the vertex buffer that make a triangle on a model. Stores the connectivity of a model.

**ISA** Instruction Set Architecture

**Management Core** The RISC-V core included in the Caravel harness, used to initialize and control the shader cores.

**PKBus** Custom multi-master multi-slave bus used exclusively in the user area. Includes an arbiter.

**PMOD** Add-on modules for Digilent FPGAs like the Arty A7 and Zedboard. Connects over 2x8 0.1" headers with a standard spacing.

**Rasterization** The process of converting continuous lines into discrete pixels on a screen.

**RTL** Register Transfer Layer, a common method to simulate hardware modules before synthesis.

**Shader** A small program that runs on a GPU.

**Shader Cores** The custom programmable cores used to run shader programs.

**Synthesis** Compiling the hardware design into logic gates and flip-flops and optimizing out unused gates. Part of the hardening process.

**Tapeout** Fabricating the final design.

**Texel** A texture pixel. One pixel in the texture image.

**Texture** An image that is applied to a model to color it. Usually there is one texture image per model.

**Texture Coordinates** The location in the texture image that corresponds to each vertex on the model. In other words, the mapping between the model and the texture.

**User Area** The part of the finished die allocated to our custom design. Has 10mm<sup>2</sup> of area. Everything else on the Caravel harness is provided to us and is not modifiable.

**Vertex** A point in 3D space.

**Vertex Buffer** List of vertices that make up a model. May also hold other metadata for each vertex, such as texture coordinates.

**Wishbone Bus** The data bus included in the Caravel harness. Connects the user area to the management core and allows the user design to be memory-mapped to the management core.

# 1 Introduction

## 1.1 Problem Statement

Many modern graphics processing units (GPUs) are heavyweight high-power products; They take up a considerable amount of space in a computational network and have a high cost. For our project, we have elected to design and test a small footprint educational GPU through the Iowa State ChipForge organization's toolflow. This organization's focus is to give students an opportunity to experience application-specific integrated circuit (ASIC) design, and the toolflow is an open-source solution to design ASICs.

Our GPU is an educational GPU in the sense that it is not the fastest or most powerful GPU solution, but it will be used to help students explore GPU design in a more consumable way than self-research and exploration. Our documentation and weekly reports can be used by students to help them understand the architecture choices we made and to help them consume the design in modularized pieces. Additionally, at Iowa State University, there is a lack of formal instruction on hardware design for graphics. CPRE 4800 "Graphics Processing and Architecture" is the only computer architecture course that gives context on GPU design, but it is seldom offered. Students at other universities may not even have a course on GPU design offered and could use this document to help themselves learn key concepts for a relatively simple GPU design.

## 1.2 Intended Users

Following is a list of potential users for a small-scale GPU.

### 1.2.1 Embedded GPU Users

As our GPU has less logic and a smaller device count, it will take less power to drive it. Thus, applications where power has to be limited, such as an embedded system, could benefit from our design. Embedded GPU Users may not necessarily be searching for the fastest or highest resolution GPU, but instead something that is low power and easy to integrate into a system. As our GPU fits on a 10mm<sup>2</sup> die, it has a very small footprint and can fit on most embedded systems with even a small amount of available space.

### 1.2.2 Chipforge Members

Members of ChipForge are students who have shown an interest in the ASIC design process. By being presented with a completed, programmable GPU design, members can dissect the choices of our group, suggest optimizations, and implement those optimizations themselves. By being presented with an educational GPU design, members can add their own ideas and

inspirations to the design. For example, a student could write a program that creates an interactive GUI or renders text on the screen, using this GPU as their hardware. Students could also create their own shaders to modify the image output.

### **1.2.3 ISU Faculty**

ISU Faculty educate a wide range of topics, and having an open-source small GPU invigorates students to create their own designs. Similar to the i281 CPU used in CPRE 2810 “Digital Logic” to motivate students to learn digital logic, our GPU can be used to motivate students in CPRE 4800 “Graphics Processing and Architecture”, CPRE 4880 “Embedded Systems Design”, or CPRE 381 “Computer Organization and Design” to show design choices and dataflow outside of the course content.

## 2 Requirements, Constraints, and Standards

### 2.1 Requirements & Constraints

#### Functional Requirements

- Must be able to render a 3D model with textures to a screen at a minimum frame rate of 15Hz

- Must support 320 x 240 resolution

- Must be able to output to a monitor over VGA

#### Technical Requirements

- Written in Verilog HDL (*constraint*)

- Maximum core clock frequency of 40 MHz (*constraint*)

- Design should pass LVS & DRC before fabrication (*constraint*)

- Must use the 130nm Skywater process (*constraint*)

- Minimum 8-bit color depth

- Minimum texture size of 16 x 16 pixels

- Must be able to render at least 4096 triangles per scene

#### User Experiential Requirements

- GPU cores must be programmable by the user

- Must be able to take commands from an outside source

- Must have a configurable output resolution

- Must have provided driver code written in C, including a full example of loading and displaying a 3D model with textures

- Must feature debug registers in critical sections of the graphics pipeline accessible from the management core

- Must provide a guide for working with the GPU

#### Physical Requirements

- Must fit in a 3mm x 3.6mm user project area (*constraint*)

- Must not use more than 38 GPIO pins (*constraint*)

- Must function nominally at room temperature

- Must not exceed maximum GPIO frequency of 50MHz (*constraint*)

## 2.2 Engineering Standards

Engineering standards ensure that across the industry, engineers agree on processes and procedures when designing products. This allows other professionals to be able to use their products better and increases the user experience by making similar products behave similarly. This allows engineers to have consistency in their work from one product to another and allows companies to build off of these standards instead of having each company recreate the standards for themselves. The following is a list of some of the IEEE standards that apply to our project.

### 2.2.1 IEEE 1364.1-2002: IEEE Standard for Verilog Register Transfer Level Synthesis

This standard describes how to write Verilog code that will be synthesized in a physical design. Our project is written in Verilog, and our goal is to receive a die of the design. Thus, our design must be able to synthesize and harden into a physically manufacturable circuit.

### 2.2.2 IEEE 1364-2001: IEEE Standard Verilog Hardware Description Language

As per the Chipfoundry flow, our design will be written in Verilog HDL. This standard defines Verilog HDL, including verification, timing, and synthesis. Thus, we must follow the standard to be able to write Verilog code that will compile, simulate, and eventually reach synthesis and layout.

### 2.2.3 IEEE 1149.7-2009: IEEE Standard for Reduced-Pin and Enhanced-Functionality Test Access Port and Boundary-Scan Architecture

This standard describes test logic for integrated circuits for multiple forms of testing, and it provides a common way to test interconnections between integrated circuits that have been placed on a printed circuit board. This is related to our project because we will have an integrated circuit that will need to be tested and will need to be able to work with other ICs on a PCB, such as memory modules and processing devices.

## 3 Project Plan

### 3.1 Project Management/Tracking Procedures

For our project, we have elected to use the waterfall project management style. This is because we have certain tapeout deadlines that must be met, such as the November and April tapeouts. Due to the nature of the chipfoundry delivery dates, we will not know if our modules are silicon-proven until after the next tapeout. Thus, we feel that the common goals of agile are not as relevant to our project, and we need to have our design mostly to fully realized before we start creating the submodules.

We track our progress by keeping a list of tasks to do and tasks completed. This list is stored in a OneNote and is updated during our weekly meetings. Additionally, our project is stored in a Git repository through GitLab, so we create branches for individual modules and use merge requests to ensure quality HDL and code is submitted.

### 3.2 Task Decomposition

1. Install toolchain and do ChipForge tutorials

- (a) Complete the blinky, UART, and Wishbone Adder tutorials

- (b) Edit the Wishbone Adder to get used to the submodule organization

- (c) Create a custom user project to understand module design from scratch

2. Define project specifications

- (a) Decide what digital ASIC we will implement

- (b) Decide and setup a specific verification method

- (c) Declare what the inputs and outputs of the software are

- (d) Declare what the inputs and outputs of the hardware are

3. Define project design

- (a) Create block diagram to describe flow of data

- (b) Define what operations happen in software and what happens in hardware

- (c) Write ISA to run on the specified cores

- (d) Decide on what peripheral modules may be needed

4. Develop hardware to run  $\mu$ GPU<sup>1</sup>

- (a) Create PMOD PCB design for external memory

- (b) Test design with FPGA SPI controller and VGA controller

5. Develop software to run  $\mu$ GPU<sup>1</sup>

- (a) Learn how to parse through Wavefront object file (.obj)

- (b) Define where data will be stored in memory

- (c) Store textures, indices, and vertices in memory

6. Write and test Verilog modules<sup>1</sup>

- (a) Assign each module to a member, and the tests for that module to another member

- (b) Write the Verilog module & SVUnit tests in parallel

- (c) Ensure module passes quality tests

- (d) Assign a 3rd and 4th person to review the module before it is merged

7. Connect and test Verilog modules in the top level design<sup>1</sup>

- (a) Once a submodule is verified, implement within a larger module

- (b) Verify the larger module with SVUnit

- (c) Ensure top level design and software work as expected

8. Test synthesis options

- (a) Ensure designs pass timing

- (b) Calculate maximum possible clock speed of GPU

- (c) Decide what PnR (Place and Route) technique should be used

9. Complete pre-check and layout

- (a) Ensure the entire GPU design fits within die area

- (b) Ensure design passes DRC (Design Rule Check) and LVS (Layout Versus Schematic)

10. Submit for tapeout

- (a) Ensure design is valid and passes Skywater DRC

- (b) Submit to chipfoundry

11. Write user guide

- (a) Write procedures for validation and bring-up once the ASIC is shipped

- (b) Write a guide on how to use the  $\mu$ GPU

<sup>1</sup>: Tasks done in parallel

### 3.3 Project Proposed Milestones, Metrics, and Evaluation Criteria

- Block Diagram

- Complete GPU block diagram with all required modules

- Get Client and Advisor approval of design

- November Tapeout

- Finish verification of rasterizer and bus components

- Add all verified designs in layout and pass DRC/LVS

- Faculty Presentation

- Finalize GPU design for presentation

- Finish Design and Verification. Begin Final Precheck

- Get entire GPU optimized to fit within die area

- April Tapeout

- Complete precheck, layout, and pass DRC/LVS

- Industry Review Panel

- Finalize Validation plan

- Complete software implementation for a visual presentation

### 3.4 Project Timeline/Schedule

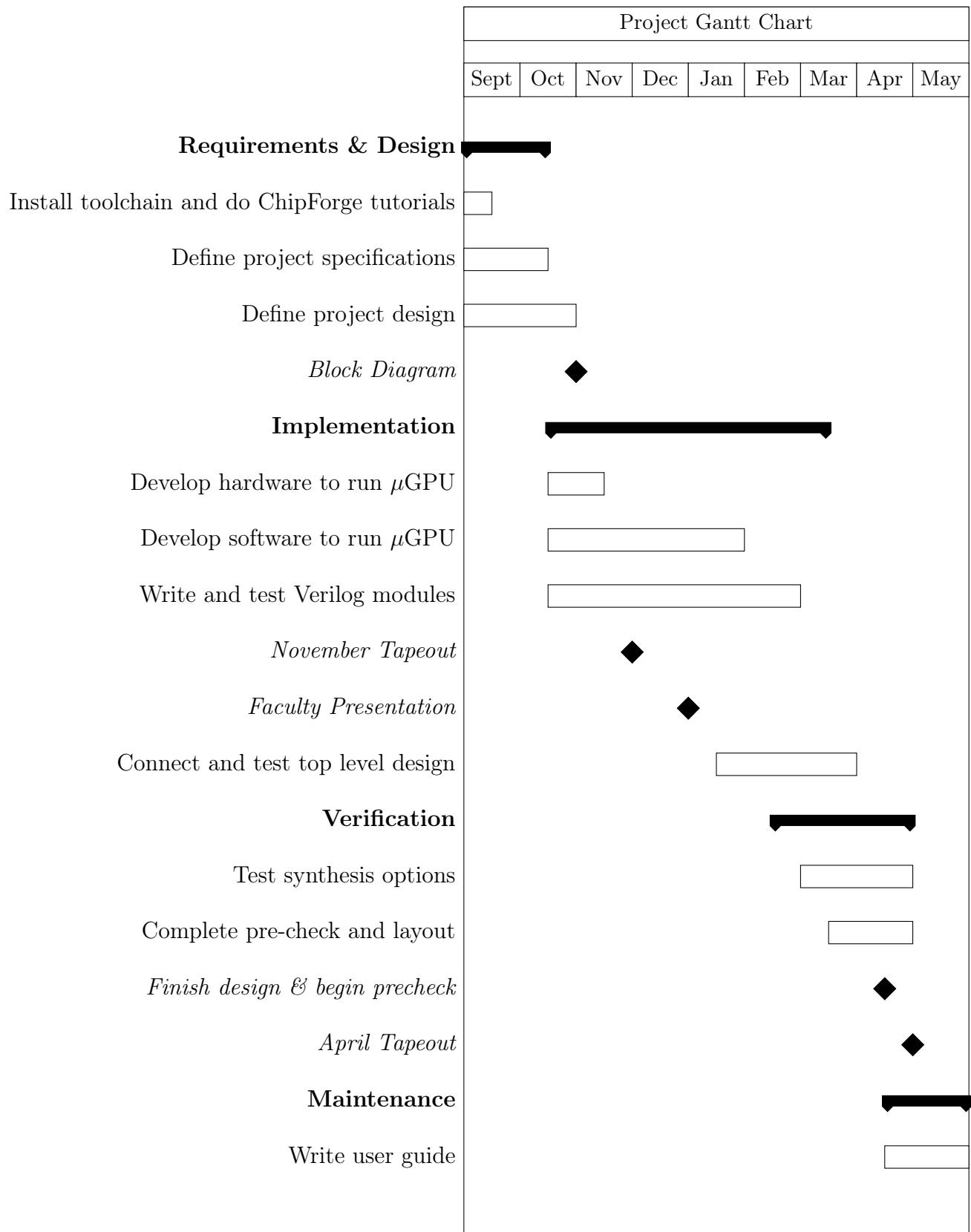

The following is a Gantt chart of the tasks listed above, with the bolded categories being waterfall groups, and diamonds being key milestones

### 3.5 Risks and Risk Management/Mitigation

Most of our major risk comes from our fabrication requirements. This includes fitting the design within the die area, meeting our functional requirements with the permitted frequency, and submitting by the tapeout deadline. Another major risk is possible errors during fabrication. There is a non-zero chance that the chip that is returned has issues that cannot be found unless exhaustive validation is done. In this case, this risk is completely out of our control, but having a validation plan can prevent further issues.

In addition to fabrication, the risks fall mainly on design and implementation. Most of these risks are simply the case that the module is not completed or a failed verification. These risks would have great consequences on the project, since every component needs to be present for the GPU to work as expected. Although the big impact has been observed, the probability that a design is not finished is much lower than other risks due to DRC, LVS, or area constraints.

Although our end goal is fabrication of the  $\mu$ GPU, the impact of fabrication risks do not make this project meaningless. The design itself will still benefit Chipforge members, allowing them to learn and build off GPU architecture. In this case, most risks are that a functional component does not work as intended. We plan on reducing these risks significantly by making sure each module is verified by a different member through SVUnit.

| Risk                                        | Probability | Project Impact |

|---------------------------------------------|-------------|----------------|

| Chipfoundry closes or doesn't allow tapeout | 5%          | High           |

| Chipfoundry deadline not met                | 10%         | High           |

| Cannot optimize design to fit the die area  | 20%         | High           |

| Cannot optimize design for 15Hz framerate   | 30%         | Medium         |

Table 1: Project Risks

### 3.6 Personnel Effort Requirements

These are the predictions of our time requirements for the  $\mu$ GPU, which is based on our initial weeks working on senior design and past ChipForge experience. This is also based on the work of previous senior design teams with projects in ASIC design.

| Task                                                     | Time Estimate (hours) |

|----------------------------------------------------------|-----------------------|

| Install toolchain and do ChipForge tutorials             | 35                    |

| Define project specifications                            | 15                    |

| Define project design                                    | 40                    |

| Develop hardware to run $\mu$ GPU                        | 20                    |

| Develop software to run $\mu$ GPU                        | 50                    |

| Write and test Verilog modules                           | 100                   |

| Connect and test Verilog modules in the top level design | 25                    |

| Test synthesis options                                   | 80                    |

| Complete pre-check and layout                            | 40                    |

| Submit for tapeout                                       | 10                    |

| Write user guide                                         | 90                    |

Table 2: Personnel Effort Requirements

### 3.7 Other Resource Requirements

Our extra resource requirements will consist mostly of the equipment that can be found in the senior design lab and Chipforge lab. This includes oscilloscopes, logic analyzers, FPGAs, and computers. All of these resources are freely available to use, so will not be a problem to attain.

## 4 Design

### 4.1 Design Context

#### 4.1.1 Broader Context

Modern GPUs are large, expensive, and power hungry. We will be providing a small form factor, energy efficient alternative to these GPUs, called a  $\mu$ GPU for our user groups. Modern GPUs are attractive to many problems due to their ability to run parallel code in their cores. We have made our pipeline programmable to allow for users to map their own problems to the  $\mu$ GPU.

Our design is to support development of ASICs and to teach about graphics pipelines to ChipForge members. Additionally, we have made the pipeline programmable so it can be mapped into courses from ISU faculty. Finally, embedded GPU users may find enjoyment in our design due to its small size and light power consumption.

Our project addresses the need for open source ASICs. ChipForge members enjoy open source ASICs because they allow members to start off with a functional code base, which allows members to see what Verilog synthesizes and what may not, and how to solve common problems. This is introducing the members to the larger open source digital design community, which will also benefit from our open source GPU design.

Additionally, some special considerations are explored in Table 3.

| Area                               | Description                                                                                                                                                                                                                                                                                     | Examples                                                                                                                                                                                                                                                     |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Public Health, Safety, and Welfare | Our project provides a small GPU that does not currently exist to most of our user groups, namely ISU Faculty and ChipForge members. Through Chipfoundry, we are lowering the barrier of access to a small scale GPU.                                                                           | The creation and distribution of a product like the $\mu$ GPU increases the job market in terms of design and testing, and marketing.                                                                                                                        |

| Global, Cultural, and Social       | Our project helps grow and support the open source digital design community, thus creating a more active digital design community. This community is an implied user group through Chipforge members and Embedded GPU enthusiasts.                                                              | By adding to the digital design community, we are growing the group and introducing ChipForge members to a larger community.                                                                                                                                 |

| Environmental                      | Our project requires silicon wafers to be manufactured, which must be mined out from the Earth and delivered to the foundry, which has a net negative environmental impact. Additionally, the chips must be shipped across the United States, increasing the environmental cost of our product. | Because the $\mu$ GPU is smaller than modern GPUs, it will have less components, thus less waste in manufacturing and when it reaches end of life. It being lighter also reduces the environmental cost of shipping, thus lowering the environmental impact. |

| Economic                           | The $\mu$ GPU is an open source design that any group could copy and modify to fit their needs. This makes the cost of development of future revisions less.                                                                                                                                    | By creating and fabricating this open source design, we are supporting the growth of small scale ASIC development. With this growth, individuals can create and market their own products, thus increasing market competition, which lowers price.           |

Table 3: Broader Context

#### 4.1.2 Prior Work/ Solutions

This project gave us the autonomy of choosing the design we wanted. When thinking of considerations, we tried to think of what would benefit Chipforge the most. Many Chipforge members have an interest in GPUs, and with the class CPRE 480: Graphics Processing and Architecture no longer being offered, a  $\mu$ GPU would provide members a great starting point for learning about GPU hardware design.

Our starting consideration was the GPU that is implemented when taking CPRE 480. The lab portion of this class involves designing a fixed graphics pipeline with rasterizer. However, with a larger team and longer timeline, this was evolved to become a multicore programmable pipeline, with vertex and fragment shading.

Rasterization is the process of turning object vectors into pixel images. Although more complex rendering methods exist today, rasterization is still commonly used due to being fast. This means the rasterizer is one of the most important modules in the  $\mu$ GPU, and it was the first module to be created. Its design was modeled after older NVIDIA rasterization techniques, which use barycentric coordinates to determine if a point is inside a triangle.

#### 4.1.3 Technical Complexity

Our design contains several components that have non-trivial amounts of complexity:

- Programmable Cores

- We need to implement what is essentially an entire processor that will handle performing any of the number of operations passed to it. We will also need to route the data in and out of it in a sensible way.

- Rasterizer

- The rasterizer will handle converting a set of 3D coordinates to an array of 2D pixels. This consists of a set of math operations that will need to be executed efficiently for performance reasons. It also handles mapping textures to the polygons.

- VGA Controller

- We decided to write our own VGA controller for better customization and integration into our overall design. Building the controller out will require properly timing output signals to display pixels within the standards established for VGA displays.

## 4.2 Design Exploration

### 4.2.1 Design Decisions

There are several important decisions that went into planning out our design:

1. Pipeline Flexibility

- For the design of our graphics pipeline, we had to decide between a fixed pipeline or a programmable one.

## 2. Design Verification Framework

- The ChipForge design flow we worked with doesn't formally have any specific verification standards. As a part of a push for better verification standards both in our senior design group and in the ChipForge extracurricular, we decided to implement a specific verification framework to use with all of our Verilog designs.

## 3. Instruction Set Architecture

- An important part of creating a programmable graphics processor is the set of instructions that the graphics processing cores will support. This includes any operations necessary support programmable operations that we are looking to make available.

## 4. Programmable Core Count

- Since we decided to make our pipeline programmable, that means that we have cores that support a range of operations. The next step in that process was deciding the number of cores.

### 4.2.2 Ideation

1. Were we to choose to build a fixed pipeline, the complexity of the pipeline would be dramatically simpler, at the cost of customization. The programmable pipeline would have more flexibility but would be much more complex to design and would be more difficult to program for as well.

2. For verification the main options we looked at and their considerations were:

- **CocoTB:** Already implemented in ChipForge's Caravel harness, and relatively easy to use.

- **SVUnit:** Lightweight and easy to implement in existing toolflow. Flexible with what simulator we use

- **UVM:** Industry standard for HDL verification. Lots of overhead for a single test, but very modular.

3. For designing our ISA, we had to look at what we needed for the various stages we would like to implement. This included operations needed to meet requirements (such as vertex shading) and operations for other goals (such as ray tracing and machine learning).

4. For deciding the number of cores the main thing we looked at was the estimated size of each core. Since we have a small die area for our  $\mu$ GPU, we decided we would fill whatever space we had left from the rest of the design with programmable cores.

### 4.2.3 Decision-Making and Trade-Off

1. We decided to proceed with designing a programmable pipeline, as programmable pipelines are more modern and better fit our users' needs. Additionally, since we have seven group members, we figured we would have a large enough labor pool to implement the programmable pipeline.

2. For the purposes of this project, we decided to integrate SVUnit into our project, as we liked its ease of use, and the simulator flexibility won us over.

3. We have yet to fully pick out our ISA, and are actively working on it.

4. We decided we want around six cores in our project, as we think this will give us a level of performance that will meet our expectations.

## 4.3 Proposed Design

### 4.3.1 Overview

Our design is a programmable GPU primarily designed for 3D rasterization. It features:

- Six (6) custom programmable cores following a custom ISA

- 16kB internal program memory

- 16 32-bit registers per core

- 48 32-bit registers shared between all cores

- Multithreading capability

- One (1) pipelined rasterizer module

- Three (3) external QSPI memory ports

- One (1) external VGA port

- One (1) external control interface

- One (1) RISC-V management core for initializing and controlling the  $\mu$ GPU

Because the design is primarily optimized for 3D rasterization it includes dedicated rasterization hardware. However it is also capable of other GPU compute tasks such as 2D rendering, ray tracing and machine learning because the custom cores are programmable. The user can write small programs in assembly that run in parallel on the cores to do virtually anything.

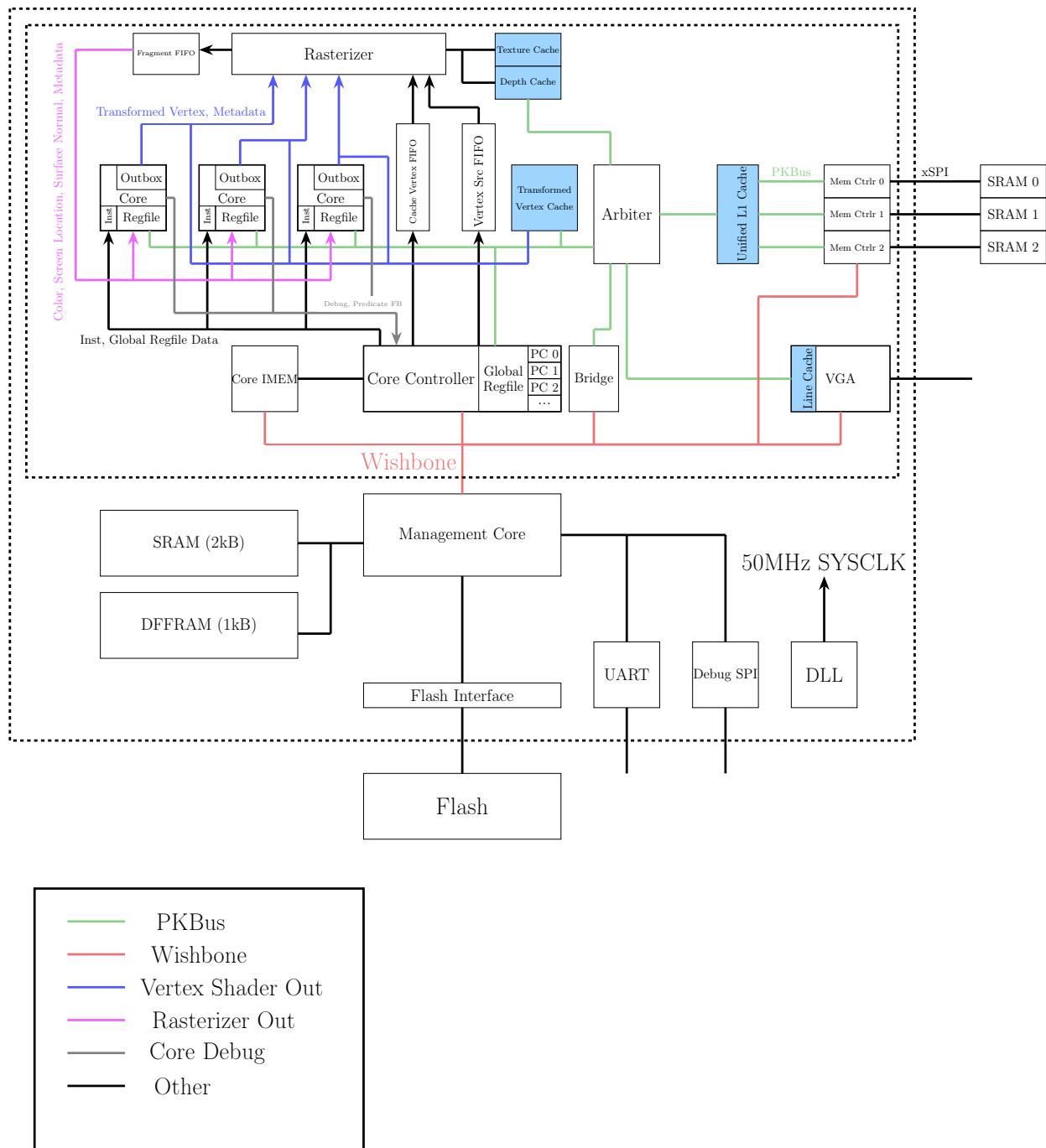

Figure 1:  $\mu$ GPU Data Flow

#### 4.3.1.1 Input Processing

3D models come in various formats, but they are all essentially a list of vertices, connectivity, and texture coordinates. The management core doesn't have enough power to process these large files. Instead, the host system that implements the  $\mu$ GPU handles preprocessing the model and converting the format.

The 3D model is stored in GPU memory and organized in the vertex buffer and index buffer. The formats of the vertex and index buffers are shown in Figure 2. Vertex buffer entries are flexible since loading a vertex is done by the shader cores and is programmable. Index buffer entries are fixed since loading is handled in hardware.

```

typedef fixed_s32_t int32_t; // Custom fixed-point type defined in hardware

// Sample vertex buffer entry without texture coordinates

typedef struct __packed {

fixed_s32_t x;

fixed_s32_t y;

fixed_s32_t z;

} vertex_t;

vertex_t vertex_buffer[N_VERTICES];

// Sample vertex buffer entry with texture coordinates

typedef struct __packed {

fixed_s32_t x;

fixed_s32_t y;

fixed_s32_t z;

fixed_s32_t tx;

fixed_s32_t ty;

} vertex_t;

vertex_t vertex_buffer[N_VERTICES];

// Index buffer entry

typedef struct __packed {

uint32_t idx[3];

} index_t;

index_t index_buffer[N_TRIANGLES];

```

Figure 2: Vertex and Index Buffer Entries for 3D Models

#### 4.3.1.2 Shader Cores

The shader cores are custom-designed pipelined cores that implement a custom ISA. They can be programmed in assembly to do anything the user wants, enabling functionality like machine learning, ray tracing, GPGPU compute, and physics simulations. The custom ISA allows the cores to implement complex functionality and pack the functionality into a single fast instruction. It currently supports vector operations (dot product, add, subtract, scale), vector loads, and pushing and pulling from the rasterizer in addition to standard scalar operations (add, subtract, add immediate, etc).

Each core has 16 word-length registers in a private register file. These hold information relevant to the data that the core is currently working on: vector coordinates, colors, normal vectors, etc. All cores also have access to 48 word-length global registers which hold common data for each model, such as the model-world-projection matrix. The register usage is defined by the user through the shader program.

The instruction memory (IMEM) and program counter (PC) is shared between all cores, meaning all cores are executing the same instruction at the same time. The complexity of individual PCs and instruction fetch logic is too much for the size of the shader cores. However, users still want to have branches and jumps in their programs. Even in basic rasterization the cores need to be split between vertex and fragment shading depending on whether there are vertices remaining in the model or fragments ready from the rasterizer.

Multithreading is handled using predication, where instead of modifying the PC for a jump or branch the execution of each instruction is dependent on a condition encoded into the instruction. In other words, each instruction has `if(predicate) { instruction }` built into the encoding. This keeps the fetch logic simple while allowing conditions. This gets more complex when introducing nested conditionals. This is addressed with a max conditional depth constant.

The following sections cover the common use cases for the shader cores in a rasterization workload. The cores are programmable and are not limited to only vertex and fragment shading, but they are most optimized for these tasks.

#### 4.3.1.2.1 Vertex Shading

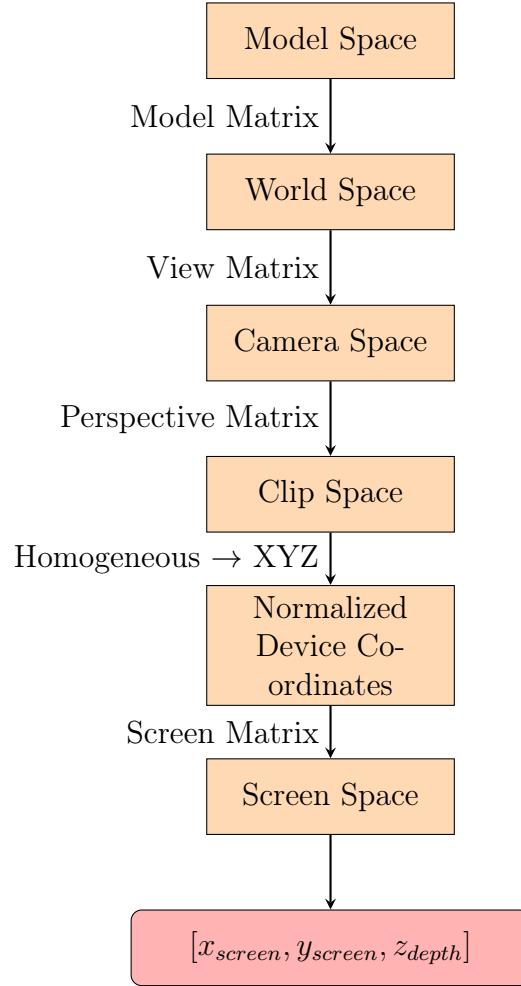

Vertex shading consists of 5 steps as shown in Figure 3. The names may be slightly different from other resources online, but this is the convention followed for the rest of this report. These steps are combined into a single matrix multiplication done in hardware using the shader cores. This is run on every vertex in every model. Vertex shading uses homogeneous coordinates, which add a fourth entry into each vector. The fourth entry is the perspective parameter, usually called  $w$ .

Figure 3: Vertex Shading Steps

1. **Model matrix:** Move, scale, stretch, and rotate the vertex from the model coordinate space (determined by the model designer, likely with the origin centered on the model) into the world space containing our scene. Some sample model matrices are shown in Table 4.

$$v_{world} = \begin{bmatrix} X_x & Y_x & Z_x & 0 \\ X_y & Y_y & Z_y & 0 \\ X_z & Y_z & Z_z & 0 \\ 0 & 0 & 0 & 1 \end{bmatrix} \begin{bmatrix} v_x \\ v_y \\ v_z \\ 1 \end{bmatrix}$$

| Matrix                                                                                                                                    | Description                                                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & \cos \theta & -\sin \theta & 0 \\ 0 & \sin \theta & \cos \theta & 0 \\ 0 & 0 & 0 & 1 \end{bmatrix}$ | Rotate by $\theta$ around the X axis.                                                                                                                                |

| $\begin{bmatrix} \cos \theta & 0 & \sin \theta & 0 \\ 0 & 1 & 0 & 0 \\ -\sin \theta & 0 & \cos \theta & 0 \\ 0 & 0 & 0 & 1 \end{bmatrix}$ | Rotate by $\theta$ around the Y axis.                                                                                                                                |

| $\begin{bmatrix} \cos \theta & -\sin \theta & 0 & 0 \\ \sin \theta & \cos \theta & 0 & 0 \\ 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 1 \end{bmatrix}$ | Rotate by $\theta$ around the Z axis.                                                                                                                                |

| $\begin{bmatrix} S_x & 0 & 0 & 0 \\ 0 & S_y & 0 & 0 \\ 0 & 0 & S_z & 0 \\ 0 & 0 & 0 & 1 \end{bmatrix}$                                    | Scale in X, Y, Z by $S_x, S_y, S_z$ . A negative scale value will reflect over the plane normal to it ( $-S_z$ reflects over the XY plane).                          |

| $\begin{bmatrix} 1 - 2a^2 & -2ab & -2ac & 0 \\ -2ab & 1 - 2b^2 & -2bc & 0 \\ -2ac & -2bc & 1 - 2c^2 & 0 \\ 0 & 0 & 0 & 1 \end{bmatrix}$   | Reflect over an arbitrary plane $ax + by + cz = 0$ .                                                                                                                 |

| $\begin{bmatrix} 1 & \tan \theta & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 1 \end{bmatrix}$                                | Skew/shear along the Y axis, angle relative to the X axis. Moving $\tan \theta$ to different locations in the matrix changes the skew direction and angle reference. |

|                                                                                                        |                                |

|--------------------------------------------------------------------------------------------------------|--------------------------------|

| $\begin{bmatrix} 1 & 0 & 0 & T_x \\ 0 & 1 & 0 & T_y \\ 0 & 0 & 1 & T_z \\ 0 & 0 & 0 & 1 \end{bmatrix}$ | Translate by $T_x, T_y, T_z$ . |

|--------------------------------------------------------------------------------------------------------|--------------------------------|

Table 4: Model Transformation Matrices

2. **View matrix:** Transform the vertex into camera space. The view matrix is the inverse of the camera matrix. The camera matrix is essentially X, Y, and Z rotation matrices multiplied with a translation matrix. This allows the camera to be positioned in all 6 degrees of freedom. Inverting the camera matrix places objects relative to the camera instead of placing the camera relative to the world coordinates. It transforms the world coordinates to be centered on the camera with the lens pointing down the -Z axis. [9] [3]

$$v_{view} = \begin{bmatrix} X_x & Y_x & Z_z & c_x \\ X_y & Y_y & Z_y & c_y \\ X_z & Y_z & Z_z & c_z \\ 0 & 0 & 0 & 1 \end{bmatrix}^{-1} v_{world}$$

3. **Perspective matrix:** Apply perspective projection, depth of field, and field of view and clip off any model features outside of a certain depth range. This creates the *viewing frustum*: a region between the near clip plane and far clip plane that defines what is displayed in the final image (as shown in Figure 4). Triangles closer to the camera than the near clip plane  $zNear$ , farther than the far clip plane  $zFar$ , or outside the frustum are not rendered. [10] [6]

Figure 4: Viewing frustum, showing  $zNear$ ,  $zFar$ , and clipping

The canonical perspective matrix with FOV calculation is shown below. After converting to normalized device coordinate (NDC) space, the output ranges for points inside the viewing frustum are  $X = [-1, 1]$ ,  $Y = [-1, 1]$ ,  $Z = [0, 1]$ .

$$v_{world} = \begin{bmatrix} x \\ y \\ z \\ 1 \end{bmatrix}$$

...where  $z$  is **negative** for all objects in front of the camera (camera points down the  $-Z$  axis).

$$v' = v_{clip}/w = v_{clip}/ -z = \begin{bmatrix} x/ -z \\ y/ -z \\ z/ -z \end{bmatrix}$$

...where dividing by  $-z$  applies perspective and corrects for the camera pointing down the -Z axis.

Applying perspective at  $zNear$ :

$$z' = \frac{\frac{-(z=-zNear) \cdot zFar - zFar \cdot zNear}{zFar - zNear}}{(w = -z = zNear)} = 0$$

Applying perspective at  $zFar$ :

$$z' = \frac{\frac{-(z=-zFar) \cdot zFar - zFar \cdot zNear}{zFar - zNear}}{(w = -z = zFar)} = 1$$

Assembling into a matrix:

$$v_{clip} = \begin{bmatrix} S & 0 & 0 & 0 \\ 0 & S & 0 & 0 \\ 0 & 0 & \frac{-zFar}{zFar - zNear} & \frac{-zFar \cdot zNear}{zFar - zNear} \\ 0 & 0 & -1 & 0 \end{bmatrix} v_{world}$$

where  $S = \frac{1}{\tan \frac{\text{fov\_radians}}{2}}$

After converting back to an ZYX 3-vector, this maps  $zNear$  to  $z = 0$  and  $zFar$  to  $z = 1$ . [6] It should be noted that this transformation is *non-linear*. The division by  $w$  creates a rational curve that gives less depth resolution when further away from  $zNear$ . This will come up later again later.

Projecting depth like this isn't helpful for our application, a range of  $[0 - 1]$  limits our depth resolution a lot. Ideally, we want to map  $zNear \rightarrow z = 0$  and  $zFar \rightarrow z = zFar - zNear$  (essentially shifting the depth of every vertex to be relative to  $zNear$  instead of relative to the camera). The modified projection matrix is shown below.

We want to modify the Z coordinate to equal what we want using a linear transformation and a division:

$$z' = \frac{az + b}{w} = \frac{az + b}{-z} = \begin{cases} 0 & \text{when } z = -zNear \\ zFar - zNear & \text{when } z = -zFar \end{cases}$$

Solving by substitution:

$$a = \frac{zFar \cdot (zFar - zNear)}{zNear - zFar} = -zFar$$

$$b = \frac{zFar \cdot zNear \cdot (zFar - zNear)}{zNear - zFar} = -zFar \cdot zNear$$

$$v_{clip} = \begin{bmatrix} S & 0 & 0 & 0 \\ 0 & S & 0 & 0 \\ 0 & 0 & -zFar & -zFar \cdot zNear \\ 0 & 0 & -1 & 0 \end{bmatrix} v_{world}$$

$$\text{where } S = \frac{1}{\tan \frac{\text{fov radians}}{2}}$$

4. **Normalized Device Coordinates (NDC):** Normalized Device Coordinates are the result of converting the perspective projection from homogeneous coordinates to an XYZ 3-vector. Normalizing the coordinate space allows the MVP matrix to scale to any display resolution or aspect ratio. As mentioned previously, the ranges are  $X = [-1, 1]$ ,  $Y = [-1, 1]$ ,  $Z = [0, 1]$ .

$$v_{ndc} = \frac{v_{clip}}{w} = \begin{bmatrix} x/w \\ y/w \\ z/w \end{bmatrix}$$

5. **Screen Matrix:** Transform the NDC into coordinates on a screen and depth into the screen. The perspective matrix and NDC moves the origin to the intersection between the  $zNear$  plane and the vector coming out the camera lens.  $+X$  points right,  $+Y$  points up, and  $+Z$  points into the screen. All monitors have their origin at the top left with  $+Y$  pointing down. We need to shift the origin and reflect across the Y axis.

This transformation can be done before or after dividing by  $w$ . In Figure 3 it's shown after, but in the final implementation it will happen before. This means all of the transformations can be combined into a single 4x4 matrix and the division at the end can be done in a single dedicated hardware module.

$$x_{screen} = x_{ndc} \frac{width}{2} + \frac{width}{2} = \frac{x_{clip} width}{w} \frac{width}{2} + \frac{width}{2}$$

$$y_{screen} = -y_{ndc} \frac{height}{2} + \frac{height}{2} = -\frac{y_{clip} width}{w} \frac{width}{2} + \frac{width}{2}$$

$$z_{screen} = z_{ndc}$$

Multiplying by  $\frac{w}{w}$ :

$$x_{screen} = x_{clip} \frac{width}{2} + \frac{width}{2}w$$

$$y_{screen} = -y_{clip} \frac{width}{2} + \frac{width}{2}w$$

Those fit perfectly in the form of a linear transformation. We can reformat to a matrix:

$$v_{screen} = \begin{bmatrix} \frac{width}{2} & 0 & 0 & \frac{width}{2} \\ 0 & -\frac{height}{2} & 0 & \frac{height}{2} \\ 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 1 \end{bmatrix} v_{clip}$$

Finally, turn the homogeneous vertex back into a 3-vector. X and Y will be the screen coordinates, Z will be the depth into the screen.

$$v_{screenXYZ} = v_{screen}/w$$

All of these matrices can be combined via matrix multiplication into a single 4x4 matrix. This matrix is called the Model-View-Perspective matrix and is provided to the shader cores by the management core. It is stored in the global registers.

The vertex shading process involves loading a vertex from the vertex buffer and applying the Model-View-Perspective matrix. After a vertex has been shaded it is pushed to the rasterizer through a FIFO using a special assembly instruction.

#### 4.3.1.2.2 Fragment Shading

Fragment shading applies lighting and post-processing to all fragments coming out of the rasterizer. The exact algorithms are flexible since the shader cores are programmable. The user could implement basic direct illumination or fancier global illumination or ray tracing algorithms. The user could also implement surface smoothing to reduce sharp edges.

The fragment shader receives the screen coordinates of a pixel, the pixel's color, and the unit normal vector of the surface containing the pixel from the rasterizer. For direct illumination, it performs a dot product to check the angle of the light relative to the normal vector. If the angle is greater than 90 degrees, the surface is facing towards the light and should be colored (the normal vector of the surface and of the light are pointing at each other). Otherwise the surface is in the shade and should be black.

$$\theta = \cos^{-1}\left(\frac{\mathbf{A} \cdot \mathbf{B}}{|\mathbf{A}||\mathbf{B}|}\right) = \cos^{-1}(\mathbf{A} \cdot \mathbf{B}) \text{ if } \mathbf{A}, \mathbf{B} \text{ are unit vectors.}$$

$$\text{Pixel} = \begin{cases} \text{Color} & \text{if } A \cdot B < 0 \\ 0 & \text{otherwise} \end{cases}$$

#### 4.3.1.3 Rasterization

The rasterizer takes in a stream of vertices from the vertex shader in sets of three. These vertices are then translated into a position on the screen. The rasterizer will determine whether the face is facing toward or away from the camera in a process called back-face culling. It will do this by determining if the vertices provided are in a clockwise or counterclockwise order. This is will be easy to implement in hardware and will allow a large portion of faces sent to the rasterizer to short-circuit.

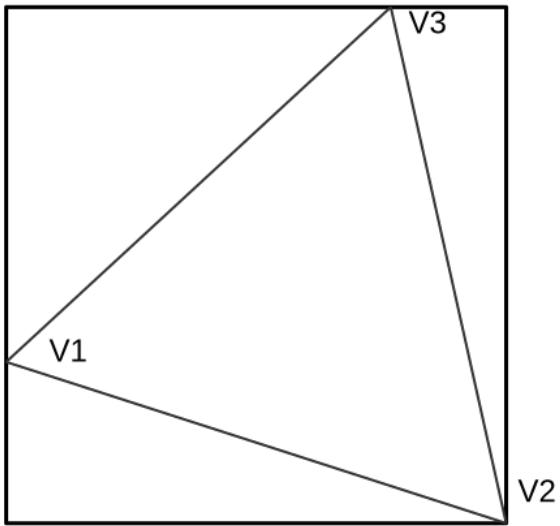

If this stage passes the upper-left and lower-right coordinates of a bounding box will be calculated for the set of vertices (Figure 5). This bounding box will be the area of pixels that must be iterated to draw the desired triangle.

Figure 5: A bounding box around a triplet of vertices

For each pixel in the bounding box the rasterizer will calculate the barycentric coordinates of the pixel within the triangle. The barycentric coordinates are the weights for a weighted average of the three coordinates of the triangle and can represent any point in the triangle. The choice to use this coordinate system works in our favor at multiple points down the pipeline and is somewhat simplistic to calculate the equations below. These coordinates are easy to use to make a decision on whether the pixel is within the triangle or not; the rasterizer can simply check to make sure all coordinates are greater than zero. If the point is not in the triangle, the rasterizer will continue by evaluating the next pixel. If the pixel is in the triangle, the rasterizer will pass this pixel down through the pipeline and continue to the next pixel.

$$\lambda_0 = \frac{(y_1 - y_2)(x - x_2) + (x_2 - x_1)(y - y_2)}{(y_1 - y_2)(x_0 - x_2) + (x_2 - x_1)(y_0 - y_2)} \quad (1)$$

$$\lambda_1 = \frac{(y_2 - y_0)(x - x_2) + (x_0 - x_2)(y - y_2)}{(y_1 - y_2)(x_0 - x_2) + (x_2 - x_1)(y_0 - y_2)} \quad (2)$$

$$\lambda_2 = 1 - \lambda_0 - \lambda_1 \quad (3)$$

Figure 6: Calculation of the barycentric coordinates for a triangle defined by  $(x_0, y_0)$ ,  $(x_1, y_1)$ ,  $(x_2, y_2)$  and a point  $(x, y)$ .

The next stage of the pipeline is the depth test stage. This stage is where the rasterizer will determine whether the new pixel is in front or behind an already drawn pixel. To do this, the depth of the currently drawn pixel needs to be evaluated. This is done by multiplying each of the barycentric coordinates ( $\lambda_0$ ,  $\lambda_1$ ,  $\lambda_2$ ) into the depth of the 3 vertices ( $z_0$ ,  $z_1$ ,  $z_2$ ) and adding the results (Figure 7). The calculated depth is then compared with a value in a special portion of memory called the depth buffer. If the evaluated value is less than that present in the depth buffer, then the current pixel passes the depth test. This means that the new value will be written back to the depth buffer for future rasterization passes, and the coordinate will be passed to the texture unit for texturing.

$$\text{Depth} = \sum_{i=0}^2 (\lambda_i \cdot z_i)$$

Figure 7: Calculation of the depth of a pixel within the rasterized triangle.

The final stage of the rasterization pipeline is the texture unit. This unit evaluates the texture address of each pixel and retrieves it from a texture buffer. The calculation of the texture pixel address is similar to the calculation of the pixel depth (Figure 8). This address can be used to index into the current texture and resolve the base color of the current pixel. This pixel and corresponding information is then sent out through a FIFO to be processes by the fragment shader.

$$t_x = \sum_{i=0}^2 (\lambda_i \cdot u_i)$$

$$t_y = \sum_{i=0}^2 (\lambda_i \cdot v_i)$$

$$\text{Texture Address} = t_y \cdot \text{Texture Width} + t_x$$

Figure 8: Calculation of the texture address for a pixel within a triangle.  $(u_{0-2}, v_{0-2})$  are the texture coordinates defined at the 3 corners of the current triangle.

#### 4.3.1.4 Buses, Memory, and Controls

The shader cores, rasterizer, VGA output, and GPU memory are memory-mapped to the management core for control and debug through the Wishbone bus. Wishbone is an open-source memory bus commonly used on FPGA projects. However, it only supports one master. The shader cores, VGA output, and GPU memory are all bus masters. Therefore we created a custom multi-master multi-slave arbitrated bus called PKBus. It is used exclusively in the user area of the design and is connected to the Wishbone bus through a bridge. Configuration registers for each peripheral are mapped to the Wishbone bus directly, but data access for GPU memory (for example) is done over PKBus.

The  $\mu$ GPU has external QSPI memory chips capable of running up to 133MHz. Graphics assets are very large, the framebuffer alone at our max resolution of 320x240 is 76.8kB. Putting memory onboard the finished die would waste valuable area and restrict our design's capabilities. External memory allows us to store more complex assets and models.

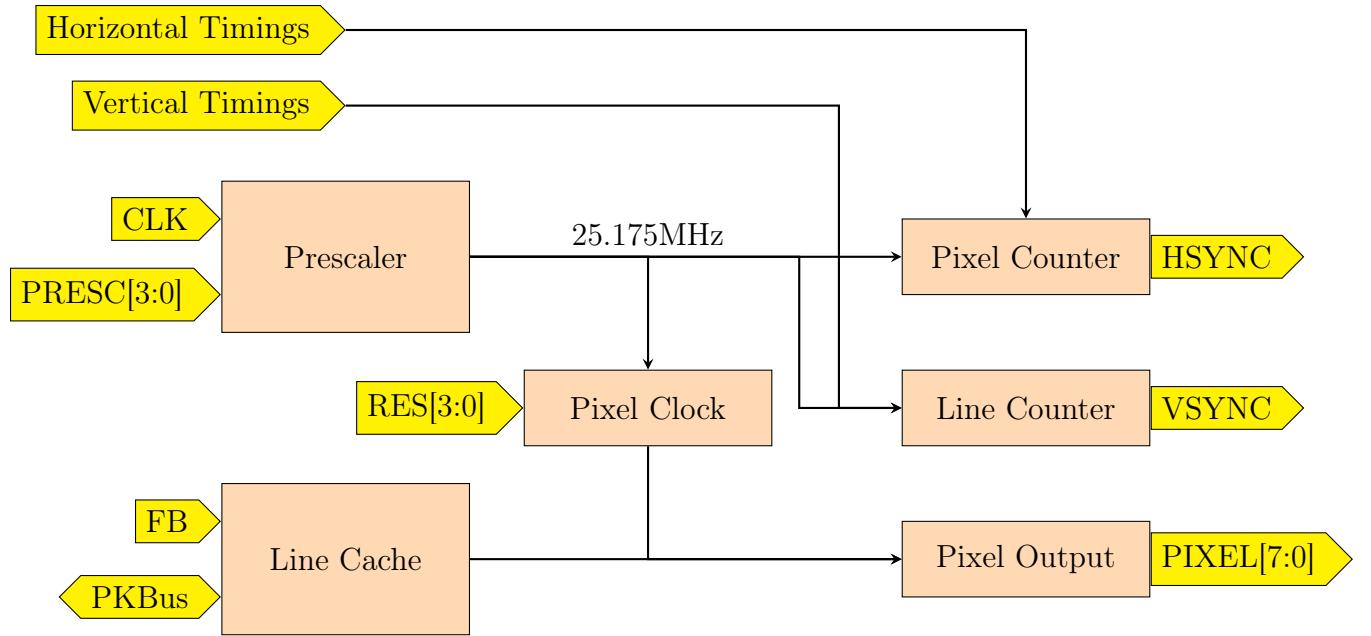

#### 4.3.1.5 VGA Output

Generating a VGA signal involves outputting the HSYNC and VSYNC signals at the correct timings and outputting color over 3 analog lines (red, green, and blue). The  $\mu$ GPU outputs 320x240 @ 60Hz using the standard timings and 8-bit color depth. 320x240 is a quarter of 640x480. The VGA output still sends out standard 640x480 timings, but performs line doubling and pixel doubling to lower the resolution. This doesn't affect overall performance since each line is read with a single burst read and cached within the VGA output module. A new line of pixels is only read *every other* line. The VGA module also supports lower resolutions: 160x120 (16th-scale) and 80x60 (64th scale).

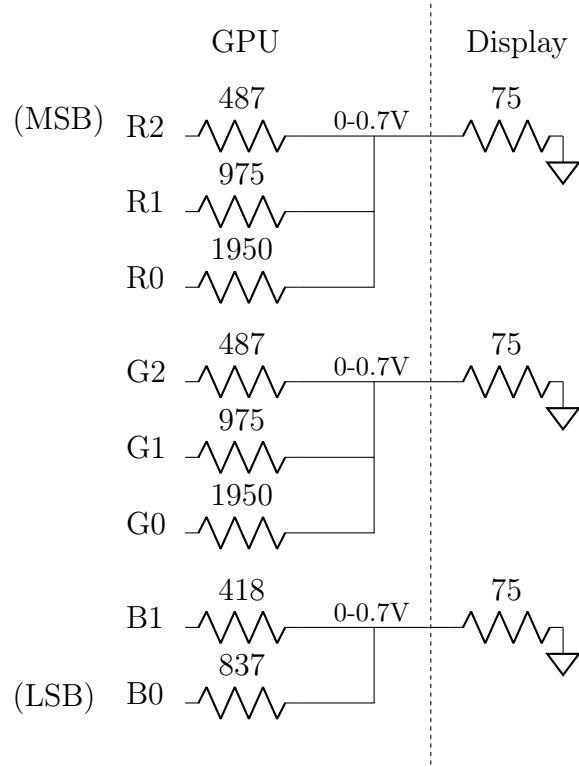

The conversion from digital 8-bit color to analog VGA color is done using a custom resistor DAC on the die (Figure 10). This saves 5 IO pins (3 for analog RGB instead of 8 for all 8 bits), which are extremely valuable on this chip. The alternative is an external resistor DAC similar to the one used for testing.

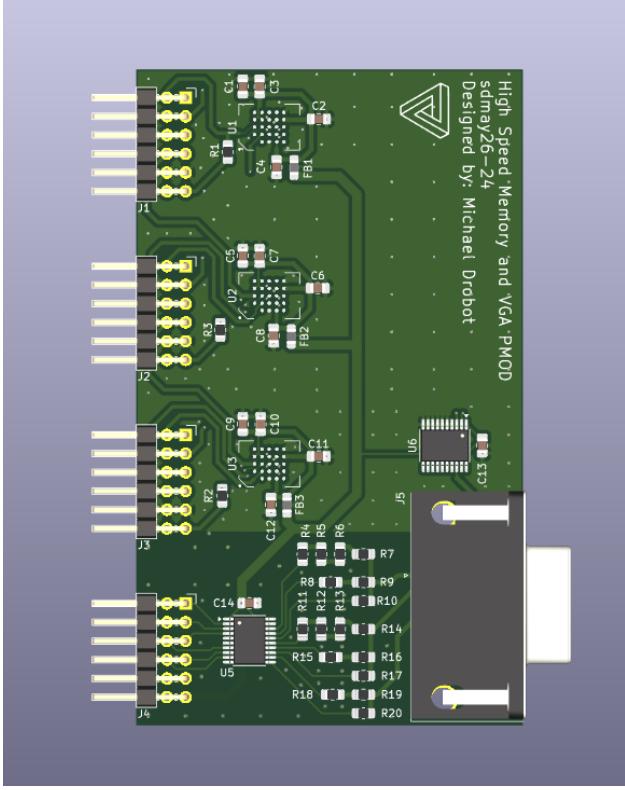

#### 4.3.1.6 Hardware

The  $\mu$ GPU needs some supporting hardware in addition to the chip design: the aforementioned external memory, a VGA connector, and headers for connecting to a host system. There are two board designs that accompany the silicon:

- **MemoryVGAPmod:** A quad PMOD board used for FPGA testing. Contains 3 QSPI memory chips, a VGA DAC, and a VGA connector.

- **$\mu$ GPU:** The carrier board for the final taped out design. Contains an M.2 slot for the Caravel board we receive from ChipFoundry, 3 QSPI memory chips, a VGA connector,

Figure 9: VGA output module block diagram

Figure 10: VGA color resistor ladder

a VGA DAC in case the onboard one doesn't work, headers for connecting to a host, and debug headers.

Figure 11: 3D render of MemoryVGAPmod

#### 4.3.2 Functionality

In a typical user environment, we would expect that users are using our product as a development or teaching platform. A user would typically use documentation provided by us as a reference to build their own application or obtain software that is already built. The user would be able to build on the software already provided by our team because of the open-source nature of the project.

We provide the user a datasheet that describes the functionality of the chip and register descriptions. Additionally, we provide an ISA summary for the shader cores that details each instruction's functionality and encoding. The build system used for the development process is open-source so bring-up should be relatively straightforward.

#### 4.3.3 Areas of Concern and Development

Our biggest concern with regards to technology is the area constraints placed on us by the multi-project wafer service, chipfoundry.io. We have  $10\text{ mm}^2$  of space on the die, which is significantly less area than any commercial graphics co-processors that we have investigated. Additionally, we have found that our process generally has a larger feature size and fewer layers than other graphics accelerators.

To attempt to combat against issues with die use we will design our system in a modular way. This will allow us to scale the processing power of the graphics core with the size of the die. This would, of course, harm performance but we are willing to make sacrifices in performance to provide a more complete and adaptable product to the user.

## 4.4 Technology Considerations

The primary technologies we will be using in our design are the SKY 130 PDK, SVUnit, EFabless Caravel, and OpenROAD. These are all open-source developments which we will use to design and fabricate our GPU. The main concern we have with these technologies is a lack of documentation and a possible lack of quality when compared with some closed-source counterparts.

We will be addressing this by attempting to use some closed-source software for our fabrication such as Cadence. This will allow us to get the most out of our PDK.

## 4.5 Design Analysis

Currently we have been making progress designing the rasterizer, memory interface, VGA controller, and Wishbone configuration system. We hope to integrate our components together soon to prepare for the upcoming November 2025 tapeout.

We believe that we will only have to make minimal modifications to our original design plan. We have been able to design a large part of the product so far and have not had any issues come up that would warrant a full design revision.

# 5 Testing

## 5.1 Unit Testing

As previously mentioned, our core module testing framework is SVUnit. Each Verilog module we create must have an SVUnit test to verify its operation and functional flow.

Additionally, all modules must pass OpenLane synthesis and hardening in the Sky130A PDK before they are merged into the codebase. RTL simulations can hide issues in the design like improper clock handling and non-procedural assignment issues. Hardening runs timing checks that ensure these issues are fixed early. Hardening also outputs the die area usage of the module. This allows us to make area-based design decisions and verify that a particular design doesn't exceed its area budget.

After passing RTL and synthesis modules must be run through gate-level (GL) simulations. GL simulations verify the synthesis results match the intended functionality. GL test support is provided with the Caravel user project.

## 5.2 Interface Testing

Interface and subsystem testing is performed with SVUnit and the Caravel test toolchain. SVUnit is used for subsystems that work independently of the management core and Wishbone bus. However, when modules need to be accessed from the management core (i.e. memory-mapped registers) it's more useful to test with the RTL test toolchain provided with the Caravel user project. This simulates the entire system: module under test, management core, firmware, and memory buses. Remaking a test framework with all of these moving parts in SVUnit would be complex and prone to issues. The Caravel test framework is well-tested and well-supported and provides high level test functionality already.

## 5.3 Integration and System Testing

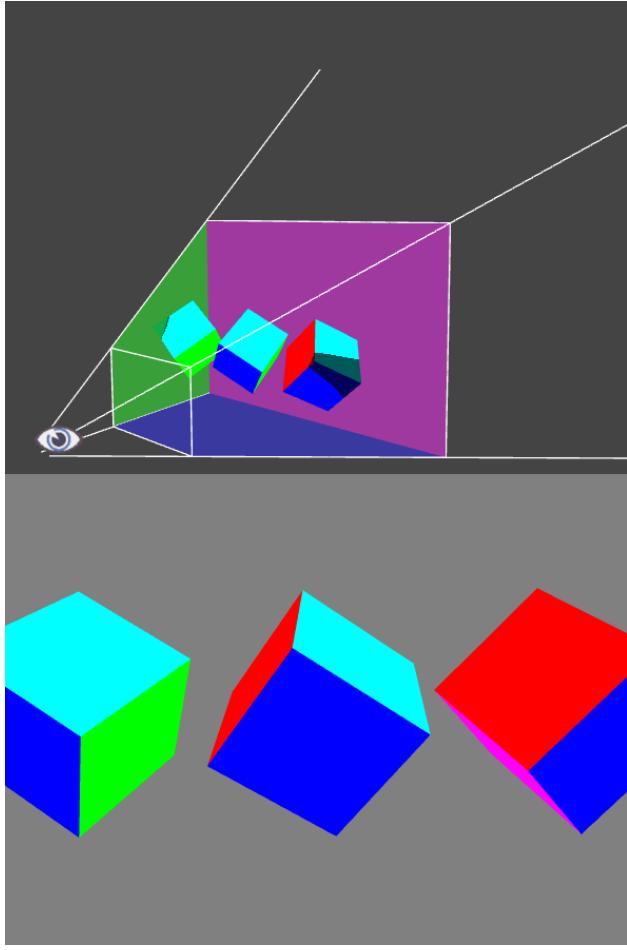

Integration testing happens in RTL simulation using the Caravel framework and on FPGAs. As mentioned previously, the Caravel framework provides a feature-rich high-level test system that works perfectly for integration testing. The framework enables us to run code on the management core to test memory-mapped registers, run shader programs on the shader cores to test functionality, and output to a virtual display to see full system output.

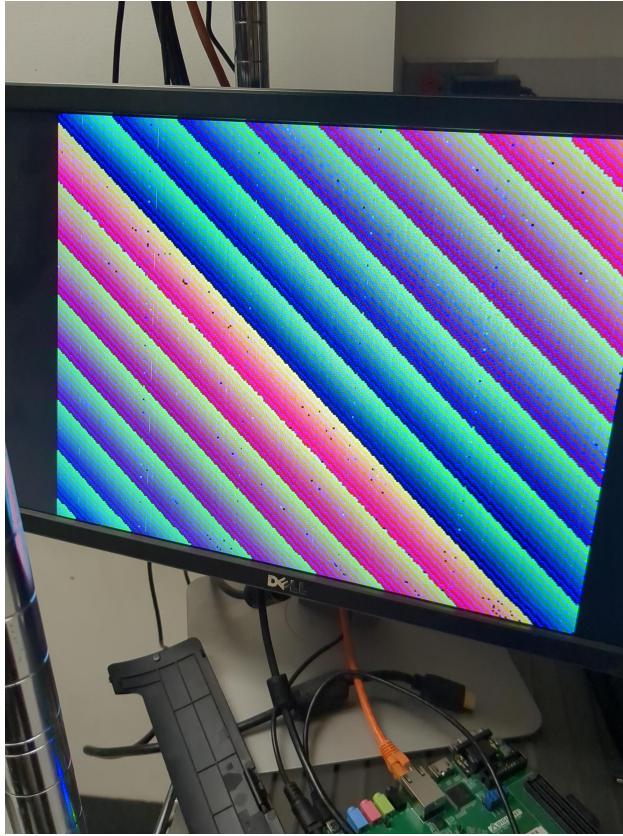

However, RTL testing doesn't always reflect the real world. There are certain components on the design that interface with external hardware (QSPI memory controller, VGA) and should be verified against the real world. ChipForge's Digilent Arty A7 FPGAs and FPGA tooling are used for this, in addition to the hardware mentioned in Section 4.3.1.6 and a Saleae Logic 8 Pro logic analyzer. In FPGA testing, we look for correct timing and framing on the memory buses and graphical artifacts or anomalies on the display. Figure 12 shows

an example of these artifacts: the intended image has clean stripes, but the monitor shows flecks of black all over the screen.

Figure 12: Monitor artifacts during FPGA testing

## 5.4 Regression Testing

Every SVUnit test exists in a common directory, and from this directory we can enter `cf_run_svunit *` in the terminal to run every unit test in the directory. Once this runs, SVUnit gives an XML of if all of the tests passed, and prints data to the console. If we see all tests have passed, we have not broken any modules.

## 5.5 Acceptance Testing

There are a number of 3D models commonly used for GPU or render engine testing. We use these models as functionality and performance benchmarks for the full design. Performance is evaluated in frames per second (FPS) rendered by the  $\mu$ GPU. Table 5 shows the test models, model source, complexity, and minimum FPS.

It should be noted that the performance of a render engine on a particular model heavily depends on the placement and orientation of the model(s) and camera. For example, if the

model is placed outside of clip space every triangle will be thrown away after the vertex shading stage. Alternatively, imagine a scene with 10 instances of the same model placed in a line with the camera pointing down the line. If the renderer renders the models farthest to closest each model will have to pass all the way through the rendering pipeline. Conversely, if the renderer starts at the front and works backward it will only render the first model and every other model will be thrown away after the depth buffer check. In short, the performance of a test is highly dependent on the exact conditions of the scene. Therefore, all models will be tested with the following position:

- Model placed at the origin, scaled appropriately to be visible on the finished image and rotated to face the  $+Z/-X$  quadrant.

- Camera placed at  $X = 0$ , translated up (towards  $+Y$ ) and out (towards  $+Z$ ) appropriately so the model is visible on the finished image.

- One model per test.

| Model                                                                               | Model Name  | Author                                            | Num. Triangles | Reqd. FPS |

|-------------------------------------------------------------------------------------|-------------|---------------------------------------------------|----------------|-----------|

|  | Cube        | Michael Drobot                                    | 12             | 24        |

|  | Suzanne [5] | Blender Foundation                                | 500            | 24        |

|  | Cow [4] [7] | Viewpoint Animation Engineering, Sun Microsystems | 5804           | 24        |

|                                                                                     |                        |                                       |        |    |

|-------------------------------------------------------------------------------------|------------------------|---------------------------------------|--------|----|

|    | Utah Teapot [8]        | Martin Newell,<br>Univ. of Utah       | 6320   | 24 |

|    | Cheburashka [1]<br>[2] | Ilya Baran,<br>Jovan Popovic,<br>MIT  | 13334  | 24 |

|   | Stanford Bunny<br>[7]  | Greg Turk, Marc Levoy, Stanford Univ. | 69451  | 10 |

|  | Stanford Dragon<br>[7] | Stanford Univ.                        | 871414 | 2  |

Table 5: Test models and required performance, by complexity

## 5.6 User Testing

It is important that the  $\mu$ GPU fits the needs of our users, and to ensure that these user needs are met we have kept in contact with most of our user bases throughout development. Notably, most members of the team are members of ChipForge, and a bulk of our work is done during ChipForge work sessions, so general members of the club are aware of the development of the  $\mu$ GPU and the features it serves.

An additional group that we are serving is the embedded GPU community. To get in touch with this group, we have done research to find common goals of products they use, such as a low power and relatively quick refresh rate. This is why we have chosen 24FPS as our standard for reasonable objects.

## 5.7 Results

Full system test results for each model are shown in Table 6.

| Rendered Image | Model Name      | Num. Triangles | FPS |

|----------------|-----------------|----------------|-----|

|                | Cube            | 12             |     |

|                | Suzanne         | 500            |     |

|                | Cow             | 5804           |     |

|                | Utah Teapot     | 6320           |     |

|                | Cheburashka     | 13334          |     |

|                | Stanford Bunny  | 69451          |     |

|                | Stanford Dragon | 871414         |     |

Table 6: Test model performance results

## 5.8 Post-Tapeout Validation

Once fabricated, each chip must be validated to test its correctness and performance. The first step would be to render the same set of 3D models on the chip and record the FPS. Although this is not an exhaustive test, successfully rendering all of the models at the target frame-rate implies no major errors. Any of the models that fail to be rendered properly require further tests.

Additional tests should target a specific functional unit. This includes running small assembly programs, specifically using a ALU, load, store, etc. and comparing the actual results to the expected results. Defects are possible during fabrication, and any of the components can be affected. If one of the cores do not work (due to a fabrication defect), a core enable bit can be cleared to prevent that core from computing. However, if the defect occurs on any other unit, that chip will most likely be unusable.

## 6 Implementation

## 7 Ethics and Professional Responsibility

### 7.1 Areas of Professional Responsibility/Code of Ethics

### 7.2 Four Principles

### 7.3 Virtues

# 8 Closing Material

## 8.1 Conclusion

## 8.2 References

- [1] Ilya Baran and Jovan Popovic. “Automatic rigging and animation of 3D characters”. In: *ACM Trans. Graph.* 26.3 (2007), p. 72. DOI: 10.1145/1276377.1276467. URL: <https://doi.org/10.1145/1276377.1276467>.

- [2] *Common 3D Test Models*. URL: <https://github.com/alecjacobson/common-3d-test-models>. (accessed: November 19, 2025).

- [3] *Computing the Pixel Coordinates of a 3D Point*. URL: <https://www.scratchapixel.com/lessons/3d-basic-rendering/computing-pixel-coordinates-of-3d-point/mathematics-computing-2d-coordinates-of-3d-points.html>. (accessed: November 19, 2025).

- [4] Douglas DeCarlo et al. “Suggestive contours for conveying shape”. In: *ACM Trans. Graph.* 22.3 (2003), pp. 848–855. DOI: 10.1145/882262.882354. URL: <https://doi.org/10.1145/882262.882354>.

- [5] *Suzanne Model*. URL: [https://projects.blender.org/blender/blender/src/branch/main/tests/files/io\\_tests/obj/suzanne\\_all\\_data.obj](https://projects.blender.org/blender/blender/src/branch/main/tests/files/io_tests/obj/suzanne_all_data.obj). (accessed: November 19, 2025).

- [6] *The Perspective and Orthographic Projection Matrix*. URL: <https://www.scratchapixel.com/lessons/3d-basic-rendering/perspective-and-orthographic-projection-matrix/building-basic-perspective-projection-matrix.html>. (accessed: November 19, 2025).

- [7] *The Stanford 3D Scanning Repository*. URL: <https://graphics.stanford.edu/data/3Dscanrep/>. (accessed: November 19, 2025).

- [8] *Utah Teapot OBJ Model*. URL: <https://graphics.stanford.edu/courses/cs148-10-summer/as3/code/as3/teapot.obj>. (accessed: November 19, 2025).

- [9] *WebGL 3D Camera*. URL: <https://webglfundamentals.org/webgl/lessons/webgl-3d-camera.html>. (accessed: November 19, 2025).

- [10] *WebGL 3D Perspective*. URL: <https://webglfundamentals.org/webgl/lessons/webgl-3d-perspective.html>. (accessed: November 19, 2025).

## 8.3 Appendices

### 8.3.1 Further Reading

Below are some helpful resources and further reading material that weren’t directly cited above. They may be helpful for getting started with a new design or debugging an existing

one.

## 1. Graphics: Rasterization, Shading, Lighting, Math

- A Trip Through the Graphics Pipeline, Fabian Giesen

- All the Pipelines - Journey Through the GPU, Lou Kramer, AMD

- An Overview of the Rasterization Algorithm, Scratchapixel

- Ray Tracing in One Weekend, Shirley, Black, Hollasch

- List of Common 3D Test Models, Wikipedia

- What Is Direct and Indirect Lighting?, JJ Kim, NVIDIA Blog

- Phong Shading, Wikipedia

## 2. Shader Cores

- From Shader Code to a Teraflop: How Shader Cores Work, Kayvon Fatahalian, SIGGRAPH 2009

- ARM Immortalis and Mali Shader Core Design

## 3. Caravel and Toolchain

- eFabless Caravel Harness Documentation

- Skywater Sky130 PDK Documentation

- OpenLANE Configuration Guide

- eFabless Design Catalog (Internet Archive)

- OpenLANE DFFRAM Macros

- OpenRAM SRAM Macro Compiler

## 9 Team

### 9.1 Team Members

### 9.2 Required Skill Sets for your Project

### 9.3 Skill Sets Covered by the Team

### 9.4 Project Management Style Adopted by the Team

### 9.5 Initial Project Management Roles

### 9.6 Team Contract